近期,三星电子在半导体工艺领域的最新进展引发了业界的广泛关注。据悉,三星在2纳米(SF2)工艺的测试生产中取得了令人瞩目的成绩,初步良品率超过了先前的预期,达到了30%的水平。这一成果为三星计划在2025年第四季度正式量产2纳米工艺,并应用于Exynos 2600的大规模生产奠定了坚实基础。

根据TECHPOWERUP的最新报道,三星2纳米工艺开发团队在实验性生产阶段取得了关键性突破。与之前的3纳米工艺相比,2纳米工艺在良品率方面的表现有了显著提升,目前已经攀升至40%以上。这一进步不仅彰显了三星在半导体工艺研发方面的实力,也为Exynos 2600的顺利量产增添了更多可能性。

然而,尽管三星在2纳米工艺上取得了显著进展,但与竞争对手台积电相比,其良品率仍有待提高。据悉,台积电在去年12月试产2纳米工艺时,良品率就已超过了60%,并传闻现已提升至70%至80%的水平,已接近量产标准。这一对比无疑给三星带来了不小的压力。

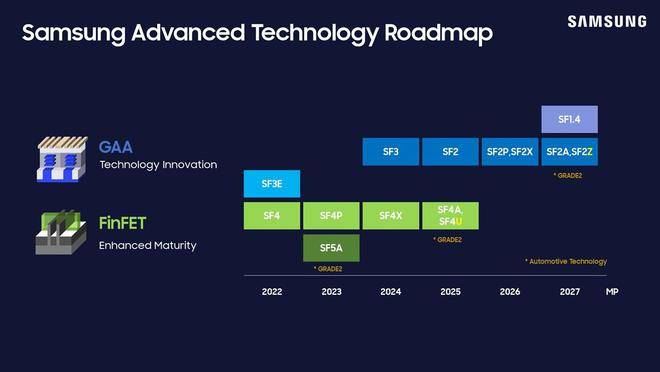

值得注意的是,三星2纳米工艺SF2集成了第三代GAA(Gate-All-Around)架构晶体管技术,相较于3纳米工艺SF3,在性能上提升了12%,功率效率提高了25%,同时芯片面积减少了5%。这些技术优势使得三星在半导体工艺领域保持了一定的竞争力。

三星还计划在2纳米制程节点上引入“BSPDN(背面供电网络)”技术。该技术通过将电源轨置于晶圆的背面,旨在消除电源线和信号线之间的瓶颈,解决FSPDN(前端供电网络)造成的前端布线堵塞问题。这一创新技术的引入有望进一步提升2纳米工艺的性能和能效,并缩小芯片面积,为三星在半导体工艺领域的未来发展注入新的活力。