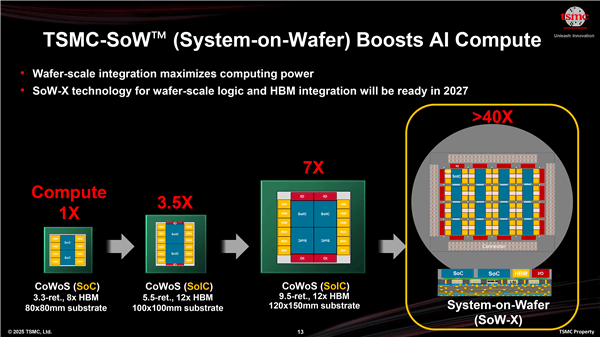

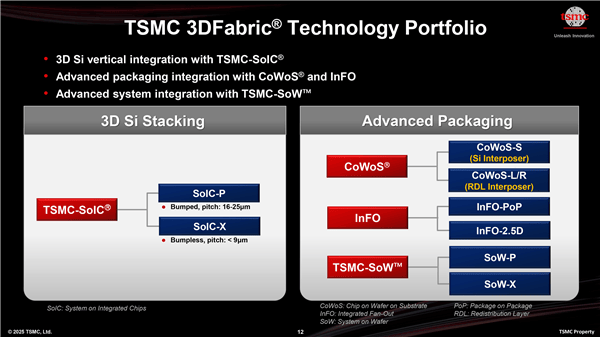

在高端计算芯片领域,随着性能需求的不断攀升,芯片尺寸也随之急剧增大。面对这一挑战,台积电正加速推进其创新的CoWoS封装技术,旨在打造前所未有的巨型芯片。据透露,该技术有望将芯片面积扩展至接近8000平方毫米,功耗达到惊人的1000瓦,而其性能则可能比传统标准处理器高出40倍之多。

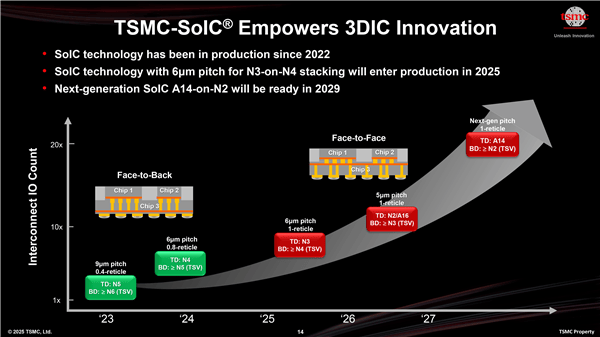

目前,台积电CoWoS封装技术的中介层面积已经能够突破至2831平方毫米,这一尺寸远超台积电光罩尺寸的极限,达到了光罩最大尺寸(约830平方毫米)的3.3倍。这一突破性的进展使得像NVIDIA B200和AMD MI300X等高性能芯片得以将大型计算模块与多个HBM内存芯片高效整合。

然而,台积电的雄心并未止步。据透露,公司计划在不久的将来推出下一代CoWoS-L封装技术,该技术将进一步扩大中介层面积至4719平方毫米,相当于光罩极限尺寸的5.5倍。为了实现这一目标,将需要使用面积达10000平方毫米的大型基板。CoWoS-L还将能够整合多达12颗HBM内存,包括即将推出的下一代HBM4。

更为惊人的是,台积电还展望了未来中介层面积可能达到7885平方毫米的愿景,这将是光罩极限尺寸的约9.5倍,并需要面积高达18000平方毫米的基板。这一前所未有的封装技术将能够容纳多达4颗计算芯片、12颗HBM内存以及其他知识产权组件,其尺寸甚至超过了一个标准的CD光盘盒。

在封装技术不断突破的同时,台积电也在积极应对巨型芯片带来的高功耗和高发热挑战。据预计,这些巨型芯片的功耗将达到1000瓦级别。为了有效管理这一巨大的功耗,台积电计划在CoWoS-L封装内的RDL中介层上直接集成一颗采用N16工艺和TSV硅通孔技术制造的电源管理IC。这一创新设计将缩短供电距离,减少有源IC数量,从而降低寄生电阻,提高系统级供电效率。

在散热方面,台积电也在积极探索直触式液冷和浸没式液冷等高效散热解决方案,以确保巨型芯片的稳定运行。

随着芯片尺寸的增大,现有的OAM模块形态也面临着挑战。目前,OAM 2.0模块的尺寸为102×165毫米,而100×100毫米的基板已经接近其极限。因此,业界需要同步制定新的OAM形态标准,以适应未来更大尺寸的芯片封装需求。

台积电在封装技术上的持续创新和突破,不仅展现了其在高端计算芯片领域的领先地位,也为未来高性能计算的发展奠定了坚实基础。随着技术的不断进步,我们有理由相信,更加高效、强大的巨型芯片将成为可能。