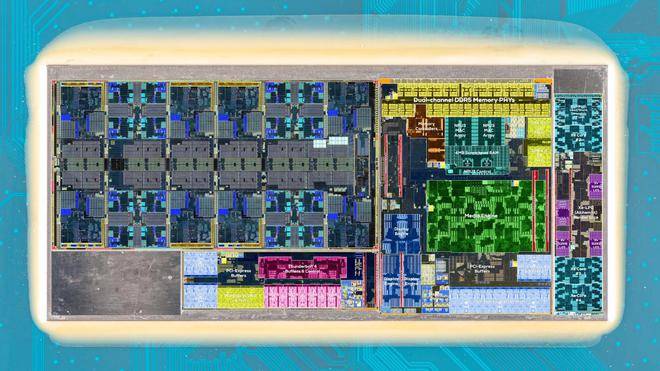

近期,芯片领域的知名分析师Andreas Schilling披露了一组英特尔Arrow Lake处理器的内部结构图,详细展示了酷睿Ultra 200S处理器的各模块布局及其Tile内部核心设计。这一披露让人们得以窥见英特尔在高性能桌面处理器领域的最新尝试。

Arrow Lake处理器作为英特尔的一次大胆创新,首次完全依赖台积电制造工艺(基板除外),并引入了复杂的Chiplet多芯片封装技术。这一技术使得处理器能够根据不同的功能需求,采用不同的制程工艺进行制造。

具体来看,Arrow Lake处理器的核心模块配置相当丰富。计算模块(Compute Tile)采用了台积电的N3B制程,面积为117.241平方毫米;输入输出模块(I/O Tile)和系统单元模块(SoC Tile)则分别使用了台积电的N6制程,面积分别为24.475平方毫米和86.648平方毫米。而核显模块(GPU Tile)则集成了4个Xe核心及Arc Alchemist渲染单元。

值得注意的是,Arrow Lake处理器的基板(BaseTile中介层)是基于英特尔自家的22nm FinFET工艺制造的,面积为302.994平方毫米。这标志着英特尔首次推出了除基板外完全由竞争对手制造的产品,展现了其在供应链合作方面的新策略。

在处理器内部,8个性能核(P-core)分布在芯片的边缘与中心区域,而16个能效核(E-core)则以四集群的形式穿插其间,挂在中央的Ring Agent环形总线上。这种设计旨在降低热密度,提高处理器的散热性能。

每个性能核都配置了3MB的L3高速缓存,总共达到了36MB。而每个能效核集群则配备了3MB的L2缓存,其中1.5MB由两个核心直接共享。英特尔此次对Arrow Lake缓存进行了重大升级,首次将能效核集群接入性能核共享的L3缓存,从而有效地提升了能效核的性能。

在功能模块方面,Arrow Lake处理器的I/O模块集成了雷电4控制器、显示PHY、PCIe Express缓冲器等多种功能;SoC模块则包含了显示引擎、媒体引擎、更多PCIe PHY、缓冲器和DDR5内存控制器等;而GPU模块则包含了四个Xe GPU内核和一个Xe LPG(Arc Alchemist)渲染处理单元。

Arrow Lake无疑是英特尔迄今为止最复杂的架构之一,也是该公司首次将Chiplet芯粒设计引入台式机桌面市场。然而,尽管采用了全新的设计,Arrow Lake系列酷睿Ultra 200S桌面处理器在游戏性能测试中并未达到预期的表现,甚至落后于14代酷睿处理器(如i9-14900K)。据分析,这主要源于其模块间的延迟问题。目前,英特尔正在积极通过固件更新来解决这一问题。