在半导体技术的最前沿,imec公司近期推出的CMOS 2.0概念正引领着一场计算领域的革命。这一创新范式旨在应对多样化应用带来的不断增长的计算需求,通过全新的系统扩展策略,挑战传统CMOS技术平台的极限。

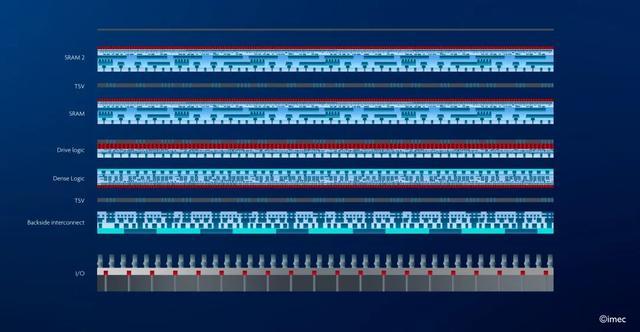

CMOS 2.0的核心在于将片上系统(SoC)划分为多个功能层,每一层都根据特定的功能需求采用最适合的技术选项构建。这一策略在系统技术协同优化(STCO)的指导下实施,确保了每一层都能发挥最大效能。例如,针对带宽和性能优化的高驱动逻辑层,以及专注于逻辑密度和性能功耗比的高密度逻辑层,它们共同构成了CMOS 2.0架构的基础。

为了实现这些功能层之间的无缝连接,imec引入了先进的3D互连技术。这种技术不仅重新定义了SoC内部异构层之间的连接方式,还让人联想到商用计算产品中已经出现的3D堆叠SRAM芯片。然而,CMOS 2.0更进一步,将异构性直接引入SoC内部,从而实现了前所未有的灵活性和性能。

在这一创新架构中,另一个关键元素是背面供电网络(BSPDN)。通过从晶圆背面为有源器件供电,BSPDN不仅消除了传统正面供电方案的局限性,还为实现极高的后端制程(BEOL)间距图案化提供了可能。这种设计使得每一层都可以集成不同类型的器件,如逻辑器件、存储器、静电放电(ESD)保护器件等,从而形成了密集的3D器件层堆叠。

为了实现CMOS 2.0的愿景,imec在3D互连和背面技术方面取得了重大突破。晶圆间混合键合技术现在能够提供亚微米互连间距连接,与BEOL最后金属层相匹配的互连密度。这一技术是实现逻辑层或存储器层堆叠的关键。同时,背面电源传输技术的发展也预示着更细粒度的连接将成为可能,任何器件技术层都将悬浮在两个独立的互连堆栈之间。

在2025年的VLSI大会上,imec展示了晶圆间混合键合和背面通孔技术的最新进展,这些技术是实现CMOS 2.0的基础。通过这些技术,imec为围绕STCO指导下的CMOS 2.0愿景设计新的系统架构奠定了坚实基础。BSPDN也被证明能够为先进系统架构带来显著的功率-性能-面积-成本(PPAC)优势。

在推动混合晶圆对晶圆键合路线图迈向200纳米间距的过程中,imec的研究人员面临了诸多挑战。随着间距的缩小,对键合覆盖层的要求也随之提高。为了实现更高的套刻精度,imec通过模拟和实验优化了键合工艺,并在实际晶圆键合前进行了光刻校正。这些努力使得imec能够实现间距为300纳米的晶圆间混合键合,且95%的芯片的套刻误差小于25纳米。

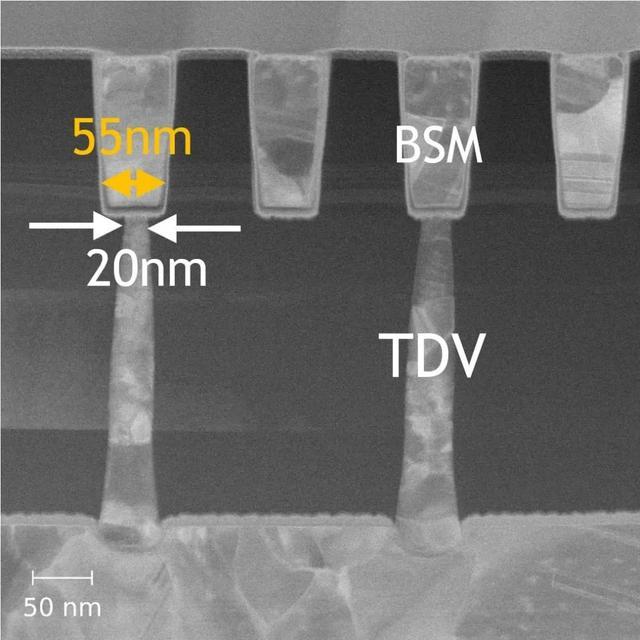

除了晶圆间混合键合外,imec还在纳米硅通孔(nTSV)技术方面取得了进展。在VLSI 2025大会上,imec展示了直径小至20纳米、间距为120纳米的背面通孔。这些通孔能够以极小的面积占用实现前后连接,为CMOS 2.0架构中的多层堆叠提供了可能。

BSPDN作为CMOS 2.0架构的另一个关键特性,通过将整个配电网络移至晶圆背面,显著降低了电源电压降,并缓解了晶圆正面的BEOL拥堵。这一技术不仅提升了性能,还减少了面积占用。在开关域设计中,BSPDN的实现方案相比传统前端PDN不仅性能更优,还减少了电源开关所占用的内核面积。

随着CMOS 2.0概念的逐步成熟,这一创新范式将为半导体生态系统中的每个参与者带来价值。通过摆脱通用CMOS技术平台的限制,CMOS 2.0将为实现更加多样化、高性能的计算系统提供新的可能。imec在这一领域的持续探索和突破,无疑将推动半导体技术迈向新的高度。